# BE-M1000 Microprocessor Datasheet

Document ID: BE-M1-DS-Eng#1204

#### 1 Introduction

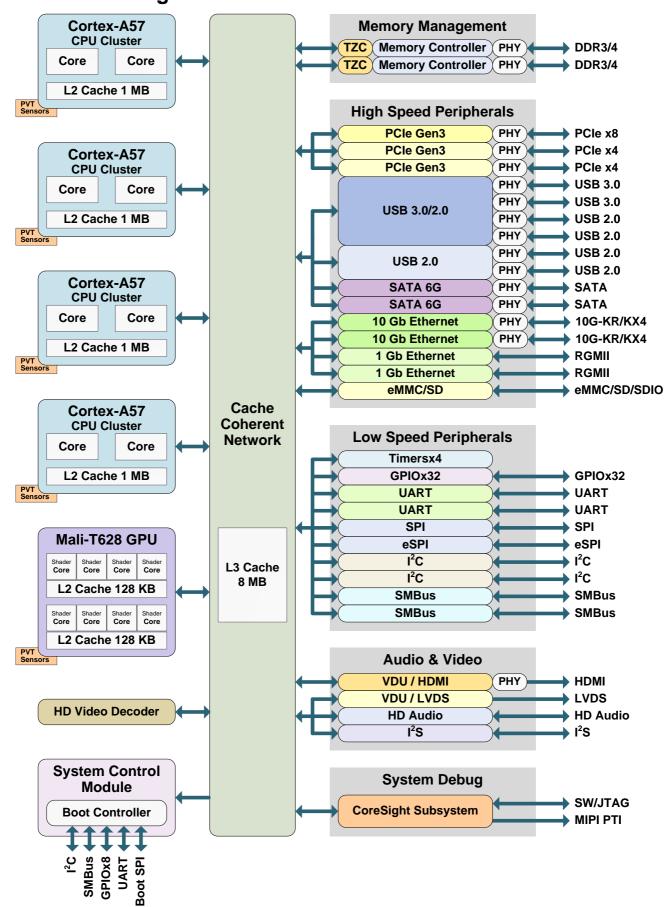

The BE-M1000 is a general purpose *System-on-a-Chip* (**SoC**) for computing systems, such as personal computers, microservers, networking equipment, multimedia and software-defined hardware, embedded systems and controllers that require high performance and low power consumption.

The SoC features eight Arm<sup>®</sup> Cortex<sup>™</sup>-A57 cores that operate at 1.5 GHz and support the coherent caches L1, L2, and L3.

The video subsystem includes two video controllers (LVDS and HDMI), and HD video decoder. Arm Mali™-T628 graphics coprocessor contains eight shader cores.

The SoC contains two DDR3/4 memory controllers and a wide range of peripheral interfaces: PCIe Gen3, 10 Gb Ethernet, 1 Gb Ethernet, USB 3.0, USB 2.0, SATA 6G, eMMC/SD, I<sup>2</sup>S, SPI, UART, I<sup>2</sup>C, GPIO, etc.

The SoC complies with Arm TrustZone® technology and capabilities necessary to build trusted systems are included.

| 1  | INTE                   | RODUCTION                     | 1  |  |  |  |  |  |

|----|------------------------|-------------------------------|----|--|--|--|--|--|

|    | 1.1                    | Main Features                 | 2  |  |  |  |  |  |

|    | 1.2                    | BLOCK DIAGRAM                 | 3  |  |  |  |  |  |

| 2  | 2 DETAILED DESCRIPTION |                               |    |  |  |  |  |  |

|    | 2.1                    | ARM CORTEX-A57 CLUSTERS       | 4  |  |  |  |  |  |

|    | 2.2                    | MEMORY MANAGEMENT             |    |  |  |  |  |  |

|    | 2.3                    | CACHE COHERENT NETWORK        |    |  |  |  |  |  |

|    | 2.4                    | SYSTEM CONTROL MODULE         |    |  |  |  |  |  |

|    | 2.5                    | HIGH SPEED PERIPHERALS        |    |  |  |  |  |  |

|    | 2.6                    | LOW SPEED PERIPHERALS         | 8  |  |  |  |  |  |

|    | 2.7                    | AUDIO & VIDEO                 | 9  |  |  |  |  |  |

|    | 2.8                    | SYSTEM MONITORING AND DEBUG   | 11 |  |  |  |  |  |

| 3  | ELEC                   | TRICAL SPECIFICATIONS         | 13 |  |  |  |  |  |

|    | 3.1                    | POWER SUPPLY PARAMETERS       | 13 |  |  |  |  |  |

|    | 3.2                    | EXTERNAL CLOCKING             | 14 |  |  |  |  |  |

| 4  | POV                    | VER-UP/DOWN                   | 19 |  |  |  |  |  |

|    | 4.1                    | Power-Up Sequence             | 19 |  |  |  |  |  |

|    | 4.2                    | Power-Down Sequence           | 21 |  |  |  |  |  |

| 5  | PIN                    | ASSIGNMENT                    | 22 |  |  |  |  |  |

|    | 5.1                    | PINOUT LIST                   | 22 |  |  |  |  |  |

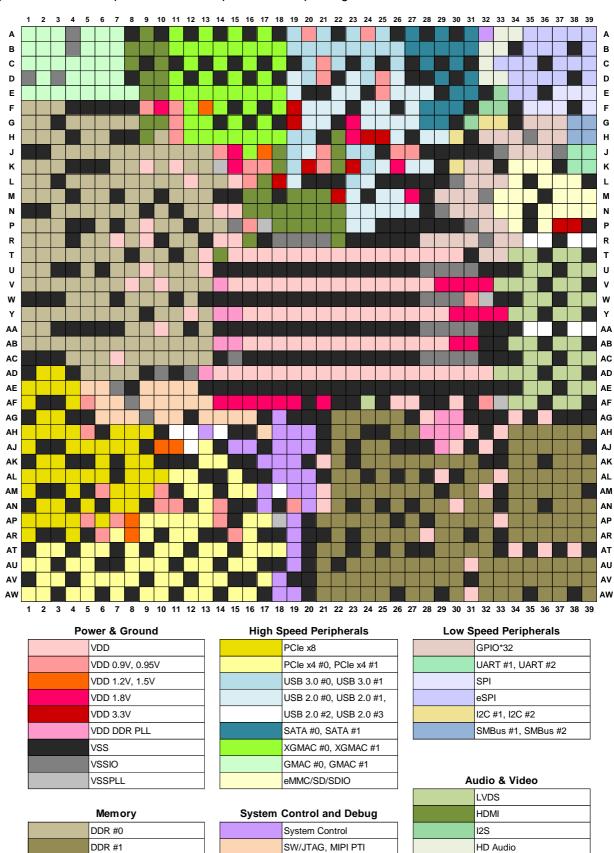

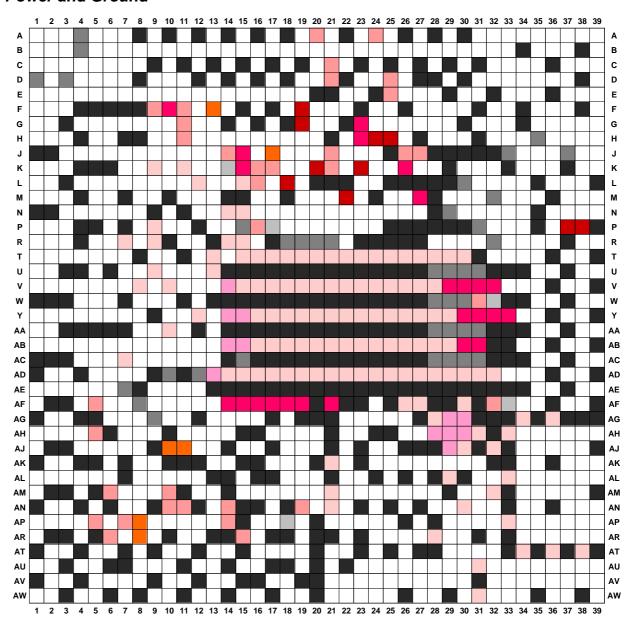

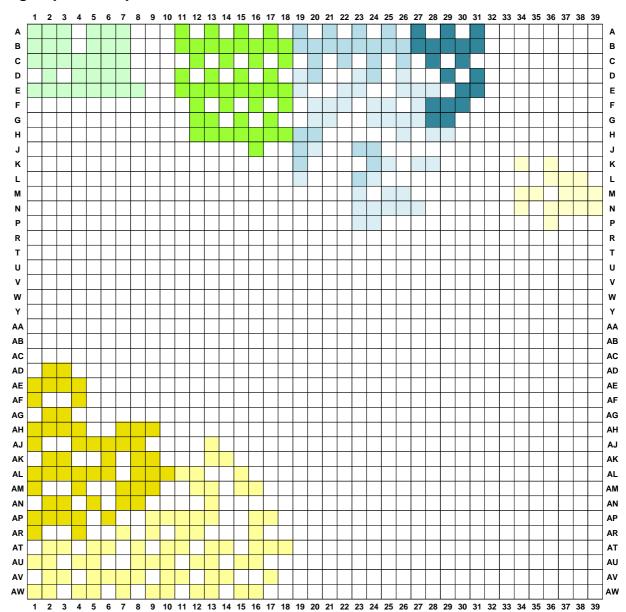

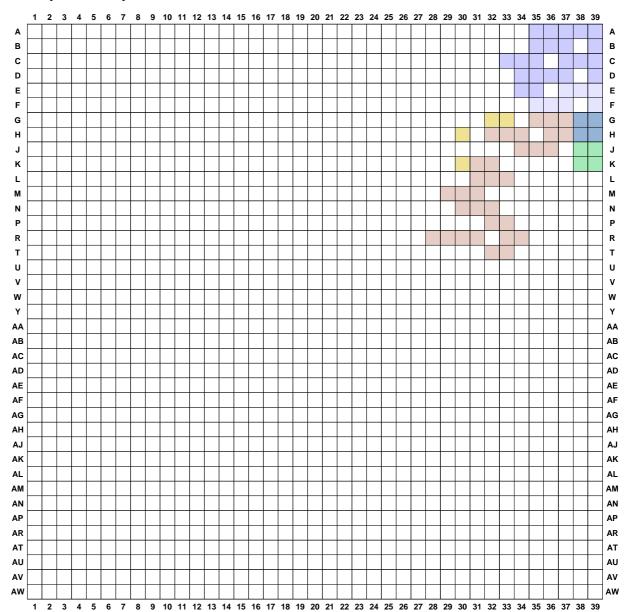

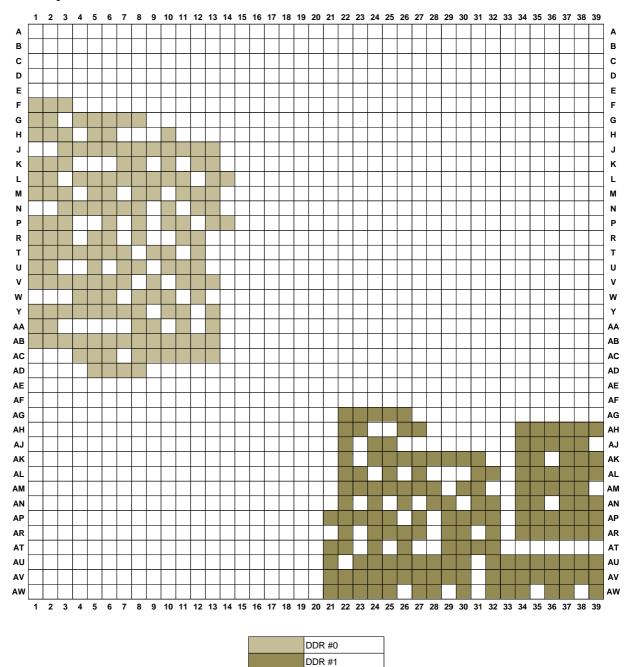

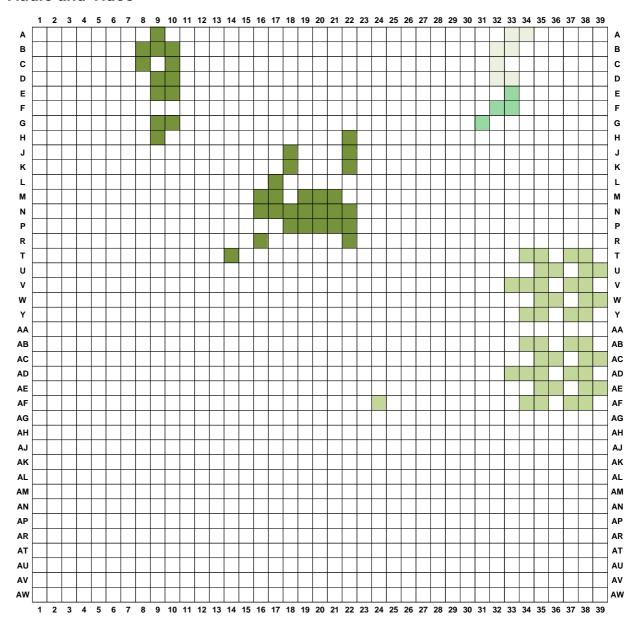

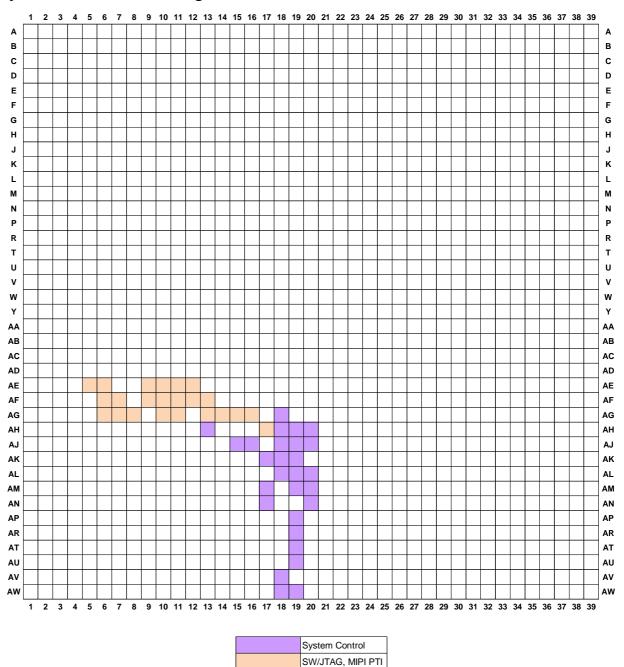

|    | 5.2                    | PIN MAP OVERVIEW              |    |  |  |  |  |  |

| 6  | PAC                    | KAGE AND ORDERING INFORMATION | 48 |  |  |  |  |  |

|    | 6.1                    | ORDERING INFORMATION          | 48 |  |  |  |  |  |

|    | 6.2                    | Marking                       | 48 |  |  |  |  |  |

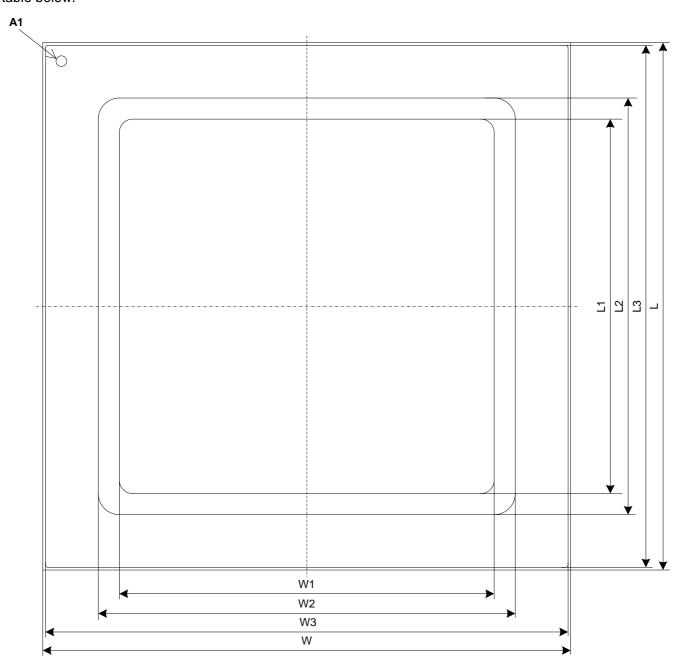

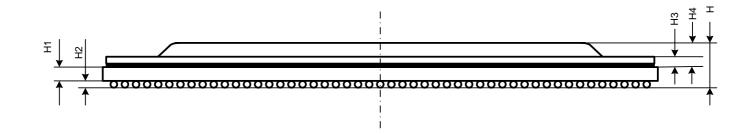

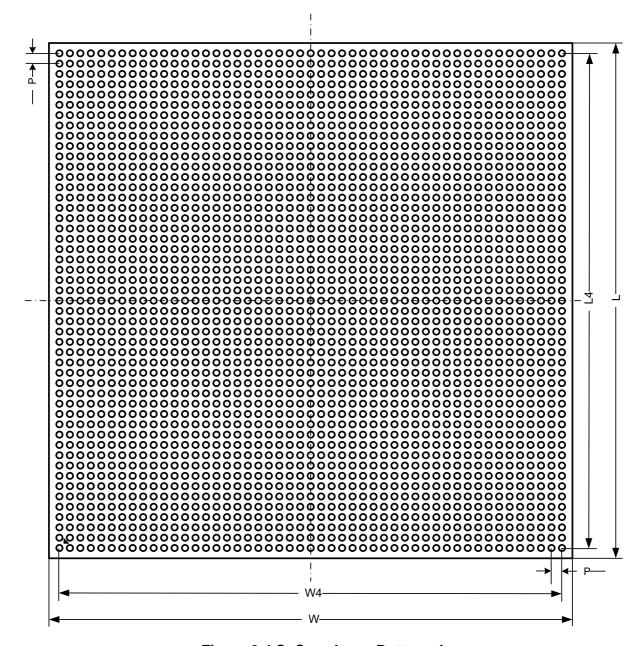

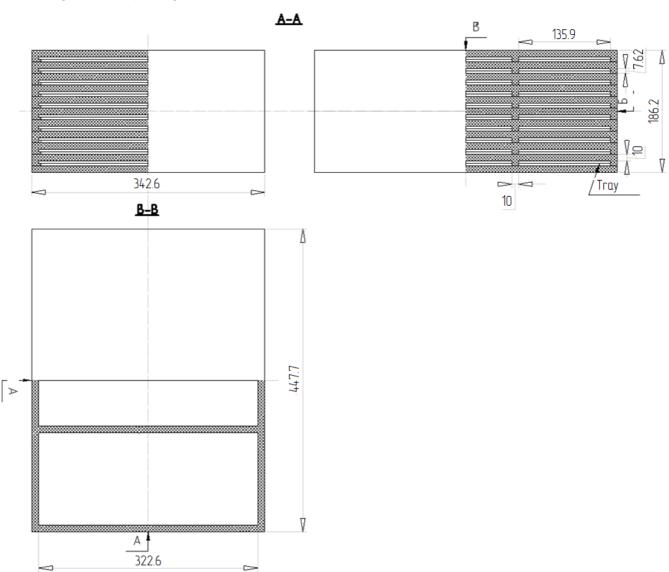

|    | 6.3                    | FCBGA-1521 PACKAGE            | 49 |  |  |  |  |  |

|    | 6.4                    | PACKING                       | 52 |  |  |  |  |  |

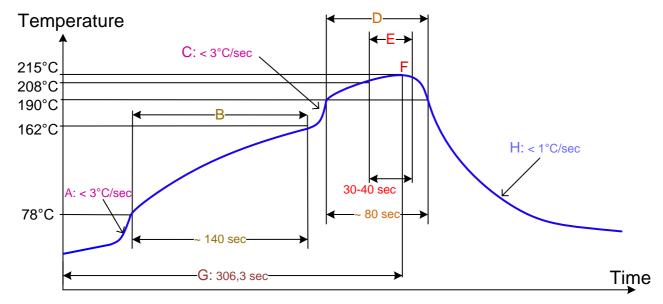

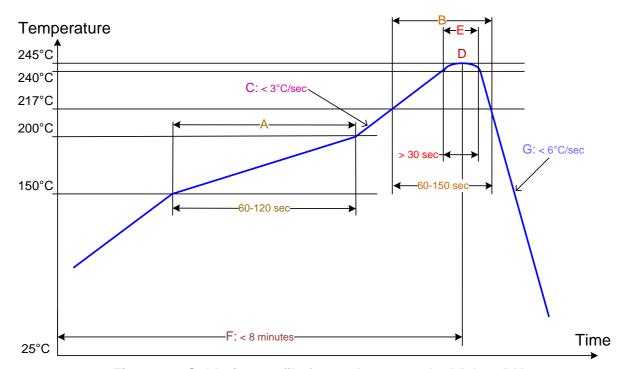

|    | 6.5                    | SOLDERING                     | 52 |  |  |  |  |  |

| 7  | SUP                    | PORT                          | 55 |  |  |  |  |  |

|    | 7.1                    | DOCUMENTATION                 | 55 |  |  |  |  |  |

|    | 7.2                    | SDK                           | 57 |  |  |  |  |  |

| C  | ONTACT                 | INFO                          | 58 |  |  |  |  |  |

| RI | EVISION                | HISTORY                       | 59 |  |  |  |  |  |

# 1.1 Main Features

**Table 1-1 Main features**

| Feature                         | Description                                                                                                                                                   |  |  |  |  |  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Armv8-A Architecture            | 8 Arm Cortex-A57 cores operating at up to 1.5 GHz                                                                                                             |  |  |  |  |  |

| Amivo-A Architecture            | 4 core clusters (2 cores and 1 MB L2 cache per cluster)                                                                                                       |  |  |  |  |  |

| Graphics Processing Unit        | Arm Mali-T628 <i>Graphics Processing Unit</i> ( <b>GPU</b> ) with 8 shader cores (two quad-core clusters) operating at 750 MHz                                |  |  |  |  |  |

|                                 | 128 KB L2 cache in a cluster                                                                                                                                  |  |  |  |  |  |

| L3 Cache                        | Cache Coherent Network (CCN) with 8 MB L3 cache memory                                                                                                        |  |  |  |  |  |

| External Memory Interface       | Two 64-bit <i>Dynamic Random Access Memory</i> ( <b>DRAM</b> ) interfaces with support of DDR4-2400/DDR3-1600 and <i>Error Correction Code</i> ( <b>ECC</b> ) |  |  |  |  |  |

|                                 | Up to 128 GB (up to 64 GB per channel)                                                                                                                        |  |  |  |  |  |

|                                 | Three PCIe Gen3 interfaces: one PCIe x8 and two PCIe x4                                                                                                       |  |  |  |  |  |

|                                 | Two USB 3.0/2.0 ports and four USB 2.0 ports                                                                                                                  |  |  |  |  |  |

| High Speed Peripheral           | Two SATA 6G subsystems                                                                                                                                        |  |  |  |  |  |

| Interfaces                      | Two 10 Gb Ethernet interfaces (10GBASE-KX4/10GBASE-KR)                                                                                                        |  |  |  |  |  |

|                                 | Two 1 Gb Ethernet RGMII                                                                                                                                       |  |  |  |  |  |

|                                 | eMMC/SD/SDIO                                                                                                                                                  |  |  |  |  |  |

|                                 | Four peripheral timers                                                                                                                                        |  |  |  |  |  |

|                                 | 32 independent GPIO lines                                                                                                                                     |  |  |  |  |  |

|                                 | Two UARTs                                                                                                                                                     |  |  |  |  |  |

| Low Speed Peripheral Interfaces | SPI                                                                                                                                                           |  |  |  |  |  |

|                                 | eSPI                                                                                                                                                          |  |  |  |  |  |

|                                 | Two I <sup>2</sup> Cs                                                                                                                                         |  |  |  |  |  |

|                                 | Two SMBus interfaces                                                                                                                                          |  |  |  |  |  |

|                                 | Independent video controller with LVDS interface                                                                                                              |  |  |  |  |  |

|                                 | Independent video controller with HDMI 2.0                                                                                                                    |  |  |  |  |  |

| Multimedia                      | HD video decoder                                                                                                                                              |  |  |  |  |  |

|                                 | HD audio controller                                                                                                                                           |  |  |  |  |  |

|                                 | I <sup>2</sup> S interface                                                                                                                                    |  |  |  |  |  |

|                                 | Arm TrustZone architecture                                                                                                                                    |  |  |  |  |  |

| Security                        | Two TrustZone controllers                                                                                                                                     |  |  |  |  |  |

|                                 | Hardware support for secure boot                                                                                                                              |  |  |  |  |  |

| System Monitoring and           | Five PVT sensor blocks                                                                                                                                        |  |  |  |  |  |

| Debug                           | Arm CoreSight™ debug and trace architecture                                                                                                                   |  |  |  |  |  |

| Package                         | FCBGA-1521 40x40 mm, 1 mm pitch, 1521 pins                                                                                                                    |  |  |  |  |  |

| Power Consumption               | 35 W max                                                                                                                                                      |  |  |  |  |  |

| Operating Temperature           | From 0 to +70°C                                                                                                                                               |  |  |  |  |  |

| Technology                      | CMOS 28 nm                                                                                                                                                    |  |  |  |  |  |

# 1.2 Block Diagram

Figure 1-1 Block diagram

# 2 Detailed Description

#### 2.1 Arm Cortex-A57 Clusters

The SoC contains 8 Arm Cortex-A57 cores in 4 clusters.

The Cortex-A57 cluster is a high-performance, low-power device that implements the <u>Armv8-A architecture</u>.

Each cluster contains two cores (up to 1.5 GHz) and L2 (1 MB) cache.

Each core contains 48 KB L1 instruction cache and 32 KB L1 data cache.

None of the cores in the clusters include optional Arm Cortex-A57 core Cryptographic Engine.

A core can operate in one of two possible states: secure and non-secure. By propagating the security state of the core through the on-chip interconnect to target-based transaction filters, the <u>TrustZone technology</u> is extended through the SoC architecture, creating a robust platform supporting fully isolated trusted and non-trusted worlds.

## 2.2 Memory Management

#### 2.2.1 DDR3/4 Memory Subsystem

The SoC supports two memory channels. Each channel contains TrustZone controller, DDR controller and DDR PHY.

Each subsystem supports the following features:

- Up to 64 GB physical memory per channel

- Up to 4 memory ranks per channel

- Integrated PHY

- Integrated TrustZone controller to provide capabilities for building trusted systems

- 64/32-bit DDR3 (speed grades up to DDR3-1600)

- 64/32-bit DDR4 (speed grades up to DDR4-2400)

- ECC: Single Error Correction/Double Error Detection (SEC/DED)

- 1:2 frequency ratio mode

- Software power management support

- Programmable support for 1T/2T memory command timing

- Software programmable Quality of Service (QoS)

- Automatic DDR3/4 low power mode operation

#### 2.2.2 DMA Controller for Low Speed Peripherals

The *DMA Controller* (**DMAC**) for <u>Low Speed Peripherals</u> implements capability of direct data transfer between a low speed device that is connected to a low speed peripheral and memory without CPU usage.

It allows to increase system performance by decreasing a load of the SoC cores.

The DMAC can only work in non-secure mode and supports the following features:

- Handshaking interfaces with two <u>UART</u>s, <u>SPI</u>, and two <u>I<sup>2</sup>C</u> controllers

- Eight unidirectional channels

- Multi-block transfers

- Single FIFO per channel for each source and destination

- Automatic data packing or unpacking to configure FIFO width

#### 2.3 Cache Coherent Network

The CCN is based on the Arm CoreLink™ CCN-504 and interconnects the main SoC subsystems and manages the Level 3 cache for these subsystems.

The CCN provides the following key features:

- Dual simplex ring-bus interconnect topology

- Broadcast snoop channel

- DVM message transport between masters

- QoS regulation for shaping traffic profiles

- Performance-related events monitoring

- Error signal gathering using an error bus, with a combined interrupt to interrupt controller

- Separate caches for secure and non-secure transactions

# 2.4 System Control Module

System control module is used to manage all SoC subsystems.

It contains the following main blocks:

- System Control Processor (SCP) that runs service functions such as:

- Starts the SoC

- Provides the initial configuration of all the SoC modules

- Monitors the state of the SoC

- Clock Management Unit (CMU) that controls system clock and reset signals

- Boot controller that contains dedicated SPI used for initial boot

- UART, SMBus, GPIOx8, and I<sup>2</sup>C controllers used for system control functions

**NOTE:** These interfaces are under SCP control and are not available for Arm Cortex A-57 cores. The interfaces can be used if they have special support from the SDK.

# 2.5 High Speed Peripherals

#### 2.5.1 PCIe Gen 3.0

The SoC contains three PCI Express (PCIe) interfaces:

- PCle x8 with 64 GT/s transfer rate

- Two PCle x4, each with 32 GT/s transfer rate

Each PCIe interface contains PCIe Root Complex controller that provides base PCIe functionality in accordance with the *PCI Express Base Specification 3.0*.

Each PCIe provides the following main features:

Integrated PHY

Revision 1.10 February 16, 2023

- Transfer rates up to 8.0 GT/s (~1GB/s) per single lane

- PCIe Active State Power Management (ASPM)

- PCle Advanced Error Reporting (AER) with multiple header logging

- Internal Address Translation Unit (iATU)

- Embedded DMA controller with four write channels and four read channels

- Automatic lane reversal

- ECRC generation and checking

- Maximum payload size:

- o 256 bytes for PCle x4

- 512 bytes for PCle x8

- One virtual channel for PCle x4, two virtual channels for PCle x8

Each PCle controller can work either in secure or non-secure modes.

#### 2.5.2 USB 3.0/2.0

The SoC contains two *Universal Serial Bus* (**USB**) controllers (USB 3.0/2.0 and USB 2.0) and six integrated PHY that provide six interfaces: two USB 3.0 interfaces and four USB 2.0 interfaces.

The USB 3.0/2.0 controller is compatible with the **xHCl Specification** by Intel Corporation. The controller is optimized for the Super-Speed applications and systems and supports the following device types:

- Super-Speed devices via USB 3.0 interface (4 Gbps IN and 4 Gbps OUT)

- High-Speed, Full-Speed, and Low-Speed devices via any interface

Each USB 3.0/2.0 interface work either in secure or non-secure mode.

The USB 2.0 controller is compatible with the **xHCl Specification** by Intel Corporation. It is optimized for the high-bandwidth applications and systems and supports the following device types:

- High-Speed (480 Mbps)

- Full-Speed (12 Mbps)

- Low-Speed (1.5 Mbps)

Each USB 2.0 interface can work either in secure or non-secure modes.

#### 2.5.3 SATA 6G

The SoC contains two identical *Serial ATA* (**SATA**) subsystems. Each SATA is compliant with **Serial ATA 3.2** and **AHCI Revision 1.3** specifications and supports the following features:

- Integrated PHY

- SATA 6.0 Gb/s speeds

- 8b/10b encoding/decoding

- Error correction code

- Power management features including automatic partial-to-slumber transition

- Embedded DMA controller with transmit and receive channels

Revision 1.10 February 16, 2023

Each SATA can work either in secure or non-secure modes.

#### 2.5.4 10 Gb Ethernet

The SoC contains two identical 10 Gb Ethernet interfaces, which enable to transmit and receive data over Ethernet in compliance with the IEEE 802.3-2008 standard for two types of 10 Gbps Ethernet: 10GBASE-KX4 and 10GBASE-KR.

Each interface contains a 10 Gb Ethernet Media Access Controller (XGMAC) with integrated 10 Gigabit Ethernet Physical Coding Sublayer (XPCS) and 10 Gb Ethernet PHY. Each XGMAC is fully compliant with clause 78 (Energy Efficient Ethernet (EEE) feature) of the IEEE 802.3az, standard for 10 Gbps operation.

Each XGMAC supports the following main features:

- Full-duplex mode at 10 Gbps

- Full compliance with Clause 71 (10GBASE-KX4) and Clause 72 (10GBASE-KR) of the IEEE 802.3-2008 standard

- Programmable frame length, supporting standard or jumbo (extendable to 16 KB) Ethernet frames

- Support for VLAN-tagged frame processing in compliance with the IEEE 802.1Q standard

- Embedded DMA controller with eight write channels and eight read channels

Each XGMAC can work either in secure or non-secure modes.

#### 2.5.5 1 Gb Ethernet

The SoC contains two identical 1 Gigabit Media Access Controllers (further GMAC).

Each GMAC enables a host to transmit and receive data over Ethernet in compliance with the IEEE 802.3-2008 standard.

Each GMAC supports the following main features:

- 10, 100, and 1000 Mbps data transfer rates with RGMII interface to communicate with an external gigabit PHY

- Full-duplex and half-duplex modes are supported

- Embedded DMA controller with transmit and receive channels

Each GMAC can work either in secure or non-secure modes.

#### 2.5.6 eMMC/SD

Embedded Multimedia Card (eMMC)/Secure Digital (SD) controller provides communication with memory cards and is compatible with the SD UHS-I and eMMC specifications. SD memory and Secure Data Input/Output (SDIO) digital interface protocol are compliant with SD HCI Specification. The eMMC supports eMMC 5.1 protocol.

The eMMC/SD controller supports the following features:

- SD-HCI host version 4 mode or less

- Embedded DMA controller

- Software tuning in SD UHS-I and eMMC modes

# 2.6 Low Speed Peripherals

#### 2.6.1 GPIOx32

The *General Purpose Input/Output* (**GPIO**) provides dedicated general-purpose pins that can be configured as either inputs or outputs. When configured as an output, you can write to an internal register to control the state driven on the output pin. When configured as an input, you can detect the state of the input by reading the state of an internal register.

The GPIO contains 32 individually controllable signals in a single port. It implements run-time 32-bit programmable interface for external communications.

#### 2.6.2 UART

There are two identical *Universal Asynchronous Receiver-Transmitters* (UART) in the SoC.

Each UART contains a handshaking interface with the <u>DMA Controller for Low Speed Peripherals</u> that can request and control non-secure data transfers between the UART and memory.

Each UART contains registers that control:

- Programmable character properties, such as:

- Number of data bits per character (5-8)

- Optional parity bit (with odd, even select or stick parity)

- o Number of stop bits (1, 1.5 or 2) Baud rates up to 1.5 Mbaud

- Parity generation/checking

- Interrupt generation

The voltage levels of the UART signals are shown in the following table.

Table 2-1 Voltage levels of the UART signals

| Voltage level    | Voltage, V |

|------------------|------------|

| Low level ("0")  | 0÷0.45     |

| High level ("1") | 1.17÷1.8   |

#### 2.6.3 SPI

The Serial Peripheral Interface (**SPI**) is a full-duplex serial master interface that supports Motorola SPI protocol. It provides short distance communication with up to four external slave SPI devices (SSx4).

The SPI controller supports the following features:

- Programmable delay on the sample time of the received serial data bit

- Dynamic control of the serial bit rate of the data transfer

- Programmable transfer data item size (4 to 16 bits)

It contains a handshaking interface with the <u>DMA Controller for Low Speed Peripherals</u> that can request and control data transfers between the SPI and memory.

#### 2.6.4 eSPI

The *Enhanced Serial Peripheral Interface* (**eSPI**) is a synchronous serial communication interface used for short distance communication with up to eight external slave devices (SSx8).

Additional eSPI signals in comparison with SPI Interface:

- RESET programmable as input or output

- ALERT input interrupts

An eSPI device communicates in full-duplex mode using master-slave architecture with up to eight external slave SPI devices (SSx8). It supports single/dual/quad SPI mode of operation.

#### $2.6.5 \, f^2C$

There are two identical general purpose *Inter-Integrated Circuit* (I<sup>2</sup>C) controllers in the SoC.

The I<sup>2</sup>C controller provides support for the communications link between the devices connected to the bus.

Each I<sup>2</sup>C controller supports the following features:

- Three modes:

- o Standard mode (0 to 100 Kb/s)

- o Fast mode (≤ 400 Kb/s) or fast mode plus (≤ 1000 Kb/s)

- o High-speed mode (≤ 3.4 Mb/s)

- Master or slave I<sup>2</sup>C operation

- 7- or 10-bit addressing

- 7- or 10-bit combined format transfers

Each I<sup>2</sup>C controller uses handshaking interface with the <u>DMA Controller for Low Speed Peripherals</u> that can request and control non-secure data transfers between the I<sup>2</sup>C and memory.

#### 2.6.6 SMBus

The SoC includes two identical System Management Bus (SMBus) interfaces.

This interface provides a two-wire bidirectional interface for transfer of bytes of information between multiple compliant I<sup>2</sup>C devices, typically with a microprocessor behind the DB-I<sup>2</sup>C master/slave controller and one or more master/slave devices.

#### 2.7 Audio & Video

#### 2.7.1 Arm Mali-T628 GPU

This *Graphic Processin Unit* (**GPU**) a complete graphics acceleration platform based on open standards. It supports 2D graphics, 3D graphics, and *General Purpose Computing on GPU* (**GPGPU**).

The graphics processor provides the following elements:

- Two clusters

- Four shader cores operating at 750 MHz per each cluster

- 128KB L2 cache per each cluster

The graphics processor provides the following main features:

Seamless load balancing across active shader cores

Revision 1.10 February 16, 2023

- The following APIs are supported:

- o OpenGL ES 1.1, 2.0, 3.0, 3.1

- o OpenCL 1.1

- RenderScript

- Full Scene Anti-Aliasing (4xFSAA, 16xFSAA) with minimal performance drop

- Adaptive Scalable Texture Compression (ASTC): Low Dynamic Range (LDR) and High Dynamic Range (HDR) are supported

- Native hardware support for 64-bit scalar and vector, integer and floating-point data

It can work both in secure and non-secure modes.

#### 2.7.2 HD Video Decoder

High Definition (HD) Video Decoder is used:

- H.265 (HEVC)

- H.264, MPEG4, MPEG2, VP8, VP6, VC1, AVS, RealVideo, and JPEG: up to 1080p at 60 fps

The decoder loads encoded video data from the system memory, decodes it and places the information ready to be sent to the video display unit into the frame buffer.

It can work either in secure or non-secure modes.

#### 2.7.3 VDU with Quad LVDS

Visual Display Unit (VDU) with quad Low-Voltage Differential Signaling (LVDS) is a general purpose display controller used to drive a wide range of display devices varying in size and capability.

The module provides the following main features:

- Display resolution up to 2560x1440 pixels

- Color resolution of up to 24 bpp

- Embedded DMA controller

- Programmable vertical and horizontal timing parameters

#### 2.7.4 VDU with HDMI 2.0

The VDU with *High Definition Multimedia Interface* (**HDMI**) provides a complete HDMI interface for transmitting video and audio data to an HDMI-compliant device, such as a computer monitor, video projector, digital television, or digital audio device.

The subsystem supports the following main features:

- Display resolution up to 2560x1440 pixels

- Color resolution of up to 24 bpp

- Embedded DMA controller

- Programmable vertical and horizontal timing parameters

- Three TMDS data channels with 6 Gbps data rate per channel

- Total maximum throughput of up to 18 Gbps (6 Gbps \* 3 channels)

Revision 1.10 February 16, 2023

- HDMI 2.0 specification features:

- o All CEA-861-F video formats

- Dynamic Range and Mastering Infoframe (DRM)

- Audio stream bit rate up to 24.576 Mbps

- It can work both in secure and non-secure modes

#### 2.7.5 HD Audio

The HD Audio controller operates with multiple input and output audio channels and interacts with external high definition audio devices. It contains DMA engines, each of which can be set up to transfer a single audio "stream" to memory from the codec or from memory to the codec depending on the DMA type.

The HD audio controller supports the following features:

- Up to four input streams

- Up to four output streams

- Two serial data outputs (SDO 0 and SDO 1 are outputs to the codecs)

- Two serial data inputs (SDI 0 and SDI 1 are inputs from the codecs)

- Up to 192 kHz sample rate

- Up to 32 bit width per stream

- Number of channels: 10 (7.1 surround sound + 2)

- Four SDO DMA engines

- Four SDI DMA engines

**NOTE:** The HD Audio controller supports only sample base rate of 48 kHz with a divider (2..8) and multiplier (2..4) for this base rate.

To support another sampling rate, for example, 44.1 or 11.025 kHz, you have to provide software resampling.

#### $2.7.6 \, l^2S$

The Inter-IC Sound (I<sup>2</sup>S) is a programmable module used for the serial communication with peripherals.

It is designed to be used in systems that process digital audio signals, such as:

- A/D and D/A converters

- Digital signal processors

- Error correction for compact disc and digital recording

- Digital filters

- Digital input/output interfaces

# 2.8 System Monitoring and Debug

#### 2.8.1 PVT Controllers

The SoC contains five *Process, Voltage and Temperature* (**PVT**) sensor blocks used to monitor PVT in the Cortex-A57 clusters and Mali-T628 GPU.

Revision 1.10 February 16, 2023

#### 2.8.2 CoreSight Subsystem

The CoreSight subsystem provides a standard implementation of the Arm Debug Interface for debug tools to work with:

- Serial Wire or JTAG Debug Port

- Trace Port Interface

The subsystem supports the following methods of debugging the SoC:

- "External" debug conventional debug through the SW/JTAG interface

- "Self-hosted" debug conventional debug with the processor running using a debug monitor that resides in memory

- Logging of hardware and software events in a trace, which is recorded in memory as well as transmitted through the *Trace Port Interface* (**MIPI PTI**) to an external debug system

It can work either in secure or non-secure modes.

# 3 Electrical Specifications

**NOTE:** The electrical characteristics are subject to change and clarification without extra notification.

# 3.1 Power Supply Parameters

BE-M1000 requires six voltage supplies and single unified ground supply as shown in the following table.

Table 3-1 BE-M1000 power domains

| Supply type                                                      | Package pin name                                                                                                                                                                                                 | Voltage, V | Max power, W |

|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|

| Core supply                                                      | VDD                                                                                                                                                                                                              |            |              |

| 0.95V voltage supply                                             | VDD_HDMI_09 VDD_USB2_09 VDD_USB3_0_09 VDD_USB3_1_09 VDD_USB3TX_0_09 VDD_USB3TX_1_09 VDD_USB3_VP_0_09 VDD_USB3_VP_1_09 VDD_PCIE4_0_09 VDD_PCIE4_1_09 VDD_PCIE8_09 VDD_SATA_09 VDD_SATATX_09 VDD_XG0_09 VDD_XG1_09 | 0.95 ± 5%  | 24           |

| PLL supply                                                       | VDDPLL_0_09 VDDPLL_1_09 VDDPLL_2_09 VDDPLL_3_09 VDDPLL_HDMI_09                                                                                                                                                   | 0.95 ± 5%  | 0.20         |

| DDR supply                                                       | VDDQ_DDR0<br>VDDQ_DDR1                                                                                                                                                                                           | 1.2 ± 5%   | 6.0          |

| VDD_PCIE4_0_15 VDD_PCIE4_1_15 VDD_PCIE8_15 VDD_XG0_15 VDD_XG1_15 |                                                                                                                                                                                                                  | 1.5 ± 5%   | 2.0          |

| Supply type          | Package pin name | Voltage, V     | Max power, W |  |  |

|----------------------|------------------|----------------|--------------|--|--|

|                      | VDD_DDR0_PLL     |                |              |  |  |

|                      | VDD_DDR1_PLL     |                |              |  |  |

|                      | VDD_HDMI_18      |                |              |  |  |

| 1.9\/ yoltogo gupply | VDD_PVT_18       | 1.8 ± 10%      | 1.8          |  |  |

| 1.8V voltage supply  | VDD_SATA_18      | 1.0 ± 10%      | 1.0          |  |  |

|                      | VDD_USB2_18      |                |              |  |  |

|                      | VDDIO_18         |                |              |  |  |

|                      | VDD_FUSE_18      |                |              |  |  |

|                      | VDD_SD_33        |                |              |  |  |

|                      | VDD_USB2_0_33    |                |              |  |  |

| 2 2\/ voltage gupply | VDD_USB2_1_33    | 3.3<br>-6.9%   | 0.7          |  |  |

| 3.3V voltage supply  | VDD_USB2_2_33    | -0.9%<br>+4.8% | 0.7          |  |  |

|                      | VDD_USB2_3_33    | 11.070         |              |  |  |

|                      | VDD_USB3_33      |                |              |  |  |

| Ground               | VSS              | 0 ± 5%         | 0            |  |  |

| Total                |                  |                | ~34.7W       |  |  |

For more information, see **Power Supply Requirements**.

# 3.2 External Clocking

## 3.2.1 Reference Clock Signals

**Table 3-2 Reference clock signals**

| Clock signal              | Pin names                       | Frequency   | Notes                            |

|---------------------------|---------------------------------|-------------|----------------------------------|

| Reference clock           | CLK25M                          | 25 MHz      |                                  |

|                           | XG0_REF_CLKN <sup>1,2</sup>     |             |                                  |

| VChE DUV reference clock  | XG0_REF_CLKP <sup>1,2</sup>     | 156.25 MHz  |                                  |

| XGbE PHY reference clock  | XG1_REF_CLKN <sup>1,2</sup>     | 130.23 WITZ |                                  |

|                           | XG1_REF_CLKP <sup>1,2</sup>     |             |                                  |

|                           | PCIE4_0_REF_CLKN <sup>1,2</sup> |             | Differential pair                |

|                           | PCIE4_0_REF_CLKP <sup>1,2</sup> |             |                                  |

| PCIe PHY reference clock  | PCIE4_1_REF_CLKN <sup>1,2</sup> | 100 MHz     | Terminated <sup>4</sup> and      |

| PCIE PHY Telefelice clock | PCIE4_1_REF_CLKP <sup>1,2</sup> | 100 MHZ     | unterminated <sup>5</sup> clocks |

|                           | PCIE8_REF_CLKN <sup>1,2</sup>   |             |                                  |

|                           | PCIE8_REF_CLKP <sup>1,2</sup>   |             |                                  |

| CATA DUV reference clock  | SATA_REFCLKP <sup>1,2</sup>     | 100 MHz     |                                  |

| SATA PHY reference clock  | SATA_REFCLKM <sup>1,2</sup>     | TUU IVIMZ   |                                  |

| Clock signal                     | Pin names                   | Frequency  | Notes             |

|----------------------------------|-----------------------------|------------|-------------------|

|                                  | USB3_0_REFCLKN <sup>3</sup> |            |                   |

| USB 3.0 PHY reference clock      | USB3_0_REFCLKP <sup>3</sup> | 100 MHz    | Differential pair |

| input                            | USB3_1_REFCLKN <sup>3</sup> | 100 WII 12 | Dillerential pail |

|                                  | USB3_1_REFCLKP <sup>3</sup> |            |                   |

|                                  | USB2_0_XI <sup>1,2</sup>    |            |                   |

|                                  | USB2_0_XO <sup>1,2</sup>    |            |                   |

| <u>USB 2.0 PHY</u> :             | USB2_1_XI <sup>1,2</sup>    |            |                   |

| XI - crystal oscillator          | USB2_1_XO <sup>1,2</sup>    | 50 MHz     |                   |

| XO - crystal oscillator or board | USB2_2_XI <sup>1,2</sup>    | 50 WITZ    |                   |

| reference clock input            | USB2_2_XO <sup>1,2</sup>    |            |                   |

|                                  | USB2_3_XI <sup>1,2</sup>    |            |                   |

|                                  | USB2_3_XO <sup>1,2</sup>    |            |                   |

| HDMI PLL reference clock input   | HDMI_PLL_27M <sup>1,2</sup> | 27 MHz     |                   |

| LVDS PLL reference clock input   | LVDS_PLL_27M <sup>1,2</sup> | 27 MHz     |                   |

#### NOTE:

- 1 If the reference clock pins are unused, they should be tied off to the ground potential.

- 2 Reference clocks connect as needed.

- 3 When one USB 3.0 port is used, a 100 MHz clock generator must be connected to the USB3\_#\_REFCLK pins. If both USB3.0 ports are not used, the USB3\_#\_REFCLK pins should be tied off to the ground potential.

- 4 With terminated clocks, a 50 Ohms termination resistor is soldered on the board close to the SoC, preventing clock reflections while providing a clock source to the PHY.

- If the board clocks are unterminated, the clock's signal level will be doubled as it hits the high-impedance input of the PHY reference clock inputs. This effect can also be used to provide a clean clock to the PHY, but ensure that the signal swing of the reference clock is not too high after the amplitude being doubled.

#### 3.2.2 Reference Clock Requirements

#### 3.2.2.1 Reference Clock (CLK25M)

Table 3-3 Reference clock (CLK25M) requirements

| Parameter                             | Min | Тур | Max | Unit |

|---------------------------------------|-----|-----|-----|------|

| Frequency range                       |     | 25  |     | MHz  |

| Reference clock frequency offset      | -50 |     | 50  | ppm  |

| Reference clock random jitter (RMS)   |     | 10  |     | ps   |

| Reference clock cycle to cycle jitter |     | 6   |     | ps   |

| Startup time                          |     | 1.5 | 3.0 | ms   |

| Disable time                          |     | 20  | 100 | ns   |

| Disable stand-by current              |     |     | 15  | uA   |

#### 3.2.2.2 SATA PHY Reference Clock

#### **Table 3-4 SATA PHY reference clock requirements**

| Parameter                             | Min    | Тур | Max    | Unit | Conditions                                                                                                       |

|---------------------------------------|--------|-----|--------|------|------------------------------------------------------------------------------------------------------------------|

| Frequency range                       |        | 100 |        | MHz  |                                                                                                                  |

| Reference clock frequency offset      | -350   |     | 350    | ppm  |                                                                                                                  |

| Reference clock random jitter (RMS)   |        |     | 3      | ps   | 1.5 MHz to Nyquist frequency.<br>For example, for 100 MHz<br>reference clock, the Nyquist<br>frequency is 50 MHz |

| Reference clock cycle to cycle jitter |        |     | 150    | ps   | DJ across all frequencies                                                                                        |

| Duty cycle                            | 40     |     | 60     | %    |                                                                                                                  |

| Common mode input level               | 0      |     | vp     | V    | Differential inputs                                                                                              |

| Differential input swing              | 0.3    |     |        | Vpp  | Differential inputs <sup>1</sup>                                                                                 |

| Single-ended input logic low          | -0.3   |     | 0.3    | V    | If single-ended input is used                                                                                    |

| Single-ended input logic high         | vp-0.3 |     | vp+0.3 | V    | If single-ended input is used                                                                                    |

| Input edge rate                       | 0.6    |     |        | V/ns |                                                                                                                  |

| Reference clock skew (±)              |        |     | 200    | ps   |                                                                                                                  |

#### 3.2.2.3 XGbE PHY Reference Clock

The PHY supports a differential reference clock source. The source may be driven through either external pads or internal pins. The chosen reference clock must meet specific requirements for signal swing and jitter. The following table summarizes the requirements of the reference clock provided to the PHY.

Table 3-5 XGbE PHY reference clock requirements

| Parameter                                         | Min  | Тур    | Max  | Unit        | Conditions                              |

|---------------------------------------------------|------|--------|------|-------------|-----------------------------------------|

| Frequency range                                   |      | 156.25 |      | MHz         |                                         |

| Frequency stability                               | -100 |        | 100  | ppm         |                                         |

| Differential input swing                          | 300  |        | 1890 | mVppd       |                                         |

| Duty cycle                                        | 40   |        | 60   | %           |                                         |

| Input edge rate                                   | 0.6  |        |      | V/ns        |                                         |

| Coupling                                          |      |        |      |             | AC coupling                             |

| Allowed jitter for 10GBASE-KR and slower          |      |        | 2.25 | ps<br>(rms) | Integrated from 12 kHz to 20 MHz        |

| Allowed jitter for 10GBASE-KX4                    |      |        | 3.6  | ps<br>(rms) | Integrated from 12 kHz to 20 MHz        |

| Peak to peak period jitter of the reference clock |      |        | 20   | ps          | Period jitter measured over 10k samples |

$<sup>^1</sup>$  VDREF\_CLK/4 + VCMREF\_CLK  $\leq$  vp + diode forward-biasing voltage and VCMREF\_CLK-VDREF\_CLK/4  $\geq$  - diode forward biasing voltage

| Parameter    | Min | Тур | Max | Unit | Conditions                                                                                                                       |

|--------------|-----|-----|-----|------|----------------------------------------------------------------------------------------------------------------------------------|

| Phase jitter |     |     | 2   | ps   | Integrated from 1.5 MHz to<br>Nyquist frequency. For example,<br>for 100 MHz reference clock, the<br>Nyquist frequency is 50 MHz |

#### 3.2.2.4 PCIe PHY Reference Clock

**Table 3-6 PCIe PHY reference clock requirements**

| Parameter                | Min  | Тур | Max  | Unit  | Conditions  |

|--------------------------|------|-----|------|-------|-------------|

| Frequency range          |      | 100 |      | MHz   |             |

| Frequency stability      | -300 |     | 300  | ppm   |             |

| Differential input swing | 300  |     | 1890 | mVppd |             |

| Duty cycle               | 40   |     | 60   | %     |             |

| Input edge rate          | 0.6  |     |      | V/ns  |             |

| Coupling                 |      |     |      |       | AC coupling |

**NOTE:** 100 MHz is the only PCIe standard compliant frequency. When using a 125 MHz frequency, the PHY may not be compliant to all PCIe specifications, such as PLL bandwidth, peaking, and jitter.

#### 3.2.2.5 USB 3.0 PHY Reference Clock

The USB 3.0 PHY supports a wide range of input clock frequencies to support both host and device applications. The following table summarizes the requirements of the reference clock provided to the USB 3.0 PHY to support superspeed only or both superspeed and high-speed operations.

Table 3-7 USB 3.0 PHY reference clock requirements

| Parameter                                 | Min  | Тур | Max  | Unit | Conditions                                                                                              |

|-------------------------------------------|------|-----|------|------|---------------------------------------------------------------------------------------------------------|

| Reference clock frequency                 |      | 100 |      | MHz  |                                                                                                         |

| Reference clock frequency stability       | -300 |     | 300  | ppm  |                                                                                                         |

| Reference clock random jitter (RMS)       |      |     | 3    | ps   | 1.5 MHz to Nyquist frequency. For example, for 100 MHz reference clock, the Nyquist frequency is 50 MHz |

| Reference clock skew                      |      |     | 200  | ps   |                                                                                                         |

| Reference clock cycle-to-<br>cycle jitter |      |     | 150  | ps   | DJ over all frequency                                                                                   |

| Duty cycle                                | 40   |     | 60   | %    |                                                                                                         |

| Common mode input level                   | 0    |     | 1.32 | V    | Differential inputs                                                                                     |

| Differential input swing                  | 0.3  |     |      | Vpp  | Differential inputs <sup>1</sup>                                                                        |

<sup>&</sup>lt;sup>1</sup> VDREF\_CLK / 4 + VCMREF\_CLK ≤ vp + diode forward biasing voltage and VCMREF\_CLK – VDREF\_CLK / 4 ≥ –diode forward biasing voltage

| Parameter                              | Min        | Тур | Max | Unit | Conditions                    |

|----------------------------------------|------------|-----|-----|------|-------------------------------|

| Single-ended input logic:<br>Low       | -0.3       |     | 0.3 | V    | If single-ended input is used |

| Single-ended input logic:<br>High      | vp-<br>0.3 |     | vp  | V    | If single-ended input is used |

| Input edge rate                        | 0.6        |     | 4   | V/ns |                               |

| Required external reference resistance |            | 200 |     | Ohms | ± 1% accuracy                 |

#### 3.2.2.6 USB 2.0 PHY Reference Clock

The USB 2.0 PHY supports the following reference clock sources:

- Crystal Oscillator connected to the USB2\_\*\_XI and USB2\_\*\_XO pins: The crystal oscillator must

have a frequency tolerance of ±400 ppm, peak jitter of ±100 ps, and an output differential voltage of

no less than 500 mV with respect to the XI signal

- External Clock connected to the USB2\_\*\_XO pin: The clock must have a fundamental frequency of 50 MHz, with a frequency tolerance of ± 400 ppm, peak jitter of ± 100 ps, duty cycle between 40/60 and 60/40 percent, and signal swing of 1.8V.

#### 3.2.2.7 HDMI PLL Reference Clock

**Table 3-8 HDMI PLL reference clock requirements**

| Parameter           | Min | Typical    | Max | Unit |

|---------------------|-----|------------|-----|------|

| Frequency range     |     | 27         |     | MHz  |

| Frequency stability | -50 |            | 50  | ppm  |

| Output              |     | LVCMOS 1.8 |     | V    |

| Duty cycle          | 40  |            | 60  | %    |

#### 3.2.2.8 LVDS PLL Reference Clock

Table 3-9 LVDS PLL reference clock requirements

| Parameter           | Min | Typical    | Max | Unit |

|---------------------|-----|------------|-----|------|

| Frequency range     |     | 27         |     | MHz  |

| Frequency stability | -50 |            | 50  | ppm  |

| Output              |     | LVCMOS 1.8 |     | V    |

| Duty cycle          | 40  |            | 60  | %    |

# 4 Power-Up/Down

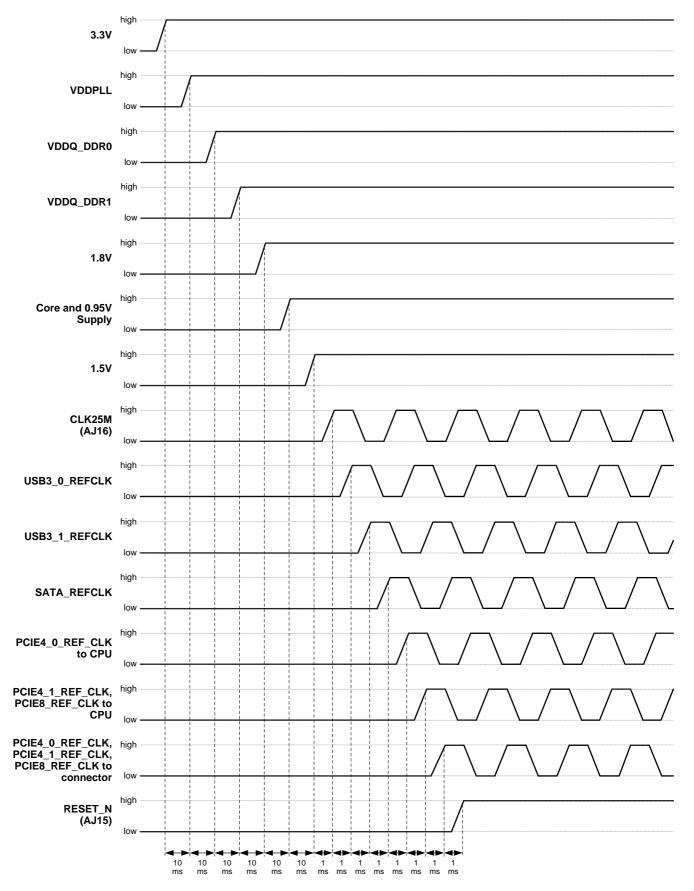

# 4.1 Power-Up Sequence

The following steps have to be performed to power up the SoC:

- 1. Provide the RESET N reset signal (active is low)

- 2. Apply voltages to power pins according to Power Supply Parameters in the following order:

- 3.3 V voltage supply

- VDDPLL

- VDDQ DDR0

- VDDQ DDR1

- 1.8 V voltage supply

- Core supply and 0.95 V voltage supply

- 1.5 V voltage supply

- 3. Provide the following reference clocks in the following order:

- CLK25M

- USB3\_0\_REFCLK

- USB3 1 REFCLK

- SATA REFCLK

- PCIE4 0 REF CLK to CPU

- PCIE4 1 REF CLK and PCIE8 REF CLK to CPU

- PCIE4 0 REF CLK, PCIE4 1 REF CLK, PCIE8 REF CLK to connector

- 4. Deassert the RESET N signal

Once the RESET\_N signal is deasserted, the boot controller provides initialization of clock and reset signals for each SoC subsystem, loads and executes the boot loader, which is stored in the boot SPI flash.

The following figure shows start sequence for BE-M1000.

Figure 4-1 Start sequence diagram for the BE-M1000

**NOTE:** The time delays shown in the figure are recommended.

# 4.2 Power-Down Sequence

To power-down, turn off power supplies from power pins according to <u>Power Supply Parameters</u> in the following order:

- 1.5 V voltage supply

- Core supply and 0.95 V voltage supply

- 1.8 V voltage supply

- VDDQ\_DDR1

- VDDQ DDR0

- VDDPLL

- 3.3 V voltage supply

# 5 Pin Assignment

## 5.1 Pinout List

The following tables contain the list of I/O pins of the SoC including the power supply and ground pins. The following legend is applied for the following tables.

Legend:

| I  | Input         |

|----|---------------|

| 0  | Output        |

| Ю  | Input/Output  |

| Α  | Analog        |

| Р  | Power supply  |

| G  | Ground        |

| NC | Not connected |

**NOTE:** Pin IDs are represented in *BE-M1000 Pinout List*. The file is available in the description of BE-M1000 on <u>Baikal Electronics website</u>.

#### 5.1.1 Memory Management

#### 5.1.1.1 DDR3/4

Table 5-1 DDR pins

| Pin name        | Туре | Description                                                                        |

|-----------------|------|------------------------------------------------------------------------------------|

| DDR0_A[13:0]    | 0    | SDRAM address                                                                      |

| DDR0_A[14]      | 0    | SDRAM WE                                                                           |

| DDR0_A[15]      | 0    | SDRAM CAS                                                                          |

| DDR0_A[16]      | 0    | SDRAM RAS                                                                          |

| DDR0_A[17]      | 0    | SDRAM A[17]                                                                        |

| DDR0_ACT_N      | 0    | When low, indicates the activate (open row) command                                |

| DDR0_ALERT_N    | I    | SDRAM CRC/parity error                                                             |

| DDR0_ATO        | Α    | Analog test output (test pad)  NOTE: Reserved in BE-M1000 manufactured since 2021. |

| DDR0_BA[1:0]    | 0    | SDRAM bank address                                                                 |

| DDR0_BG[1:0]    | 0    | SDRAM bank group                                                                   |

| DDR0_CK[3:0]    | 0    | SDRAM clock                                                                        |

| DDR0_CK_N[3:0]  | 0    | SDRAM clock                                                                        |

| DDR0_CKE[3:0]   | 0    | SDRAM clock enable                                                                 |

| DDR0_CS_N[3:0]  | 0    | SDRAM chip select                                                                  |

| DDR0_DM[8:0]    | Ю    | SDRAM data mask                                                                    |

| DDR0_DQ[63:0]   | Ю    | SDRAM data                                                                         |

| DDR0_DQS[8:0]   | Ю    | SDRAM data strobe                                                                  |

| DDR0_DQS_N[8:0] | Ю    | SDRAM data strobe                                                                  |

| Pin name        | Туре | Description                                                                                                          |

|-----------------|------|----------------------------------------------------------------------------------------------------------------------|

| DDR0_DTO[1:0]   | 0    | Digital test output (test pad)  NOTE: Reserved in BE-M1000 manufactured since 2021.                                  |

| DDR0_ECC[7:0]   | Ю    | SDRAM data ECC                                                                                                       |

| DDR0_MIRROR     | 0    | SDRAM mirror (optional DIMM signal)                                                                                  |

| DDR0_ODT[3:0]   | 0    | SDRAM on-die termination                                                                                             |

| DDR0_PARITY     | 0    | SDRAM parity                                                                                                         |

| DDR0_QCSEN_N    | 0    | SDRAM quad CS enable (optional DIMM signal)                                                                          |

| DDR0_RAM_RST_N  | 0    | SDRAM reset                                                                                                          |

| DDR0_VREFI[9:0] | Α    | IO ring VREFI net  NOTE: Reserved in BE-M1000 manufactured since 2021.                                               |

| DDR0_VREFI_ZQ   | Α    | IO ring VREFI ZQ net                                                                                                 |

| DDR0_ZQ         | А    | ZQ resistor (to external calibration resistor) Connects the pin through an external 240 ± 1% Ohms resistor to ground |

| DDR1_A[13:0]    | 0    | SDRAM address                                                                                                        |

| DDR1_A[14]      | 0    | SDRAM WE                                                                                                             |

| DDR1_A[15]      | 0    | SDRAM CAS                                                                                                            |

| DDR1_A[16]      | 0    | SDRAM RAS                                                                                                            |

| DDR1_A[17]      | 0    | SDRAM A[17]                                                                                                          |

| DDR1_ACT_N      | 0    | When low, indicates the activate (open row) command                                                                  |

| DDR1_ALERT_N    | I    | SDRAM CRC/parity error                                                                                               |

| DDR1_ATO        | А    | Analog test output (test pad)  NOTE: Reserved in BE-M1000 manufactured since 2021.                                   |

| DDR1_BA[1:0]    | 0    | SDRAM bank address                                                                                                   |

| DDR1_BG[1:0]    | 0    | SDRAM bank Group                                                                                                     |

| DDR1_CK[3:0]    | 0    | SDRAM clock                                                                                                          |

| DDR1_CK_N[3:0]  | 0    | SDRAM clock                                                                                                          |

| DDR1_CKE[3:0]   | 0    | SDRAM clock enable                                                                                                   |

| DDR1_CS_N[3:0]  | 0    | SDRAM chip select                                                                                                    |

| DDR1_DM[8:0]    | Ю    | SDRAM data mask                                                                                                      |

| DDR1_DQ[63:0]   | Ю    | SDRAM data                                                                                                           |

| DDR1_DQS[8:0]   | Ю    | SDRAM data strobe                                                                                                    |

| DDR1_DQS_N[8:0] | Ю    | SDRAM data strobe                                                                                                    |

| DDR1_DTO[1:0]   | 0    | Digital test output (test pad)  NOTE: Reserved in BE-M1000 manufactured since 2021.                                  |

| DDR1_ECC[7:0]   | Ю    | SDRAM data ECC                                                                                                       |

| DDR1_MIRROR     | 0    | SDRAM mirror (optional DIMM signal)                                                                                  |

| Pin name        | Туре | Description                                                                                                          |

|-----------------|------|----------------------------------------------------------------------------------------------------------------------|

| DDR1_ODT[3:0]   | 0    | SDRAM on-die termination                                                                                             |

| DDR1_PARITY     | 0    | SDRAM parity                                                                                                         |

| DDR1_QCSEN_N    | 0    | SDRAM quad CS enable (optional DIMM signal)                                                                          |

| DDR1_RAM_RST_N  | 0    | SDRAM reset                                                                                                          |

| DDR1_VREFI[9:0] | Α    | IO ring VREFI net  NOTE: Reserved in BE-M1000 manufactured since 2021.                                               |

| DDR1_VREFI_ZQ   | А    | IO ring VREFI ZQ net                                                                                                 |

| DDR1_ZQ         | Α    | ZQ resistor (to external calibration resistor) Connects the pin through an external 240 ± 1% Ohms resistor to ground |

## 5.1.2 High Speed Peripherals

#### 5.1.2.1 PCIe x8

### Table 5-2 PCle x8 pins

| Pin name           | Туре | Description                                                                                                                                                                              |

|--------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCIE8_AMON0        | 0    | Analog monitor bump  NOTE: Reserved in BE-M1000 manufactured since 2021.                                                                                                                 |

| PCIE8_AMON1        | 0    | Analog monitor bump  NOTE: Reserved in BE-M1000 manufactured since 2021.                                                                                                                 |

| PCIE8_ATT_BUT      | ı    | Indicates whether the system attention button is pressed  NOTE: Reserved in BE-M1000 manufactured since 2021.                                                                            |

| PCIE8_ATT_IND[1:0] | 0    | Controls the system attention indicator <b>NOTE:</b> Reserved in BE-M1000 manufactured since 2021.                                                                                       |

| PCIE8_CMD_INT      | ı    | Hot-plug controller command completed interrupt  NOTE: Reserved in BE-M1000 manufactured since 2021.                                                                                     |

| PCIE8_DMON0        | 0    | NOTE: Reserved in BE-M1000 manufactured since 2021.                                                                                                                                      |

| PCIE8_DMON1        | 0    | NOTE: Reserved in BE-M1000 manufactured since 2021.                                                                                                                                      |

| PCIE8_DMONB0       | 0    | NOTE: Reserved in BE-M1000 manufactured since 2021.                                                                                                                                      |

| PCIE8_DMONB1       | 0    | NOTE: Reserved in BE-M1000 manufactured since 2021.                                                                                                                                      |

| PCIE8_INTRL_CTRL   | 0    | NOTE: Reserved in BE-M1000 manufactured since 2021.                                                                                                                                      |

| PCIE8_INTRL_ENG    | ı    | System Electromechanical Interlock Engaged  NOTE: Reserved in BE-M1000 manufactured since 2021.                                                                                          |

| PCIE8_MRL_SENS     | I    | Manually-Operated Retention Latch (MRL) sensor state Indicates the state of the MRL sensor:  • 0: MRL is closed  • 1: MRL is opened  NOTE: Reserved in BE-M1000 manufactured since 2021. |

| Pin name           | Туре | Description                                                                               |

|--------------------|------|-------------------------------------------------------------------------------------------|

| PCIE8_PRES_ST      | I    | Presence detect state  NOTE: Reserved in BE-M1000 manufactured since 2021.                |

| PCIE8_PWR_CTRL     | 0    | Controls the system power controller  NOTE: Reserved in BE-M1000 manufactured since 2021. |

| PCIE8_PWR_FAULT    | I    | Power fault detect  NOTE: Reserved in BE-M1000 manufactured since 2021.                   |

| PCIE8_PWR_IND[1:0] | 0    | Controls the system power indicator  NOTE: Reserved in BE-M1000 manufactured since 2021.  |

| PCIE8_RBIAS0       | Ю    | Bias resistor bump  Connects to 1 kOhms ± 1% precision resistor on board                  |

| PCIE8_RBIAS1       | Ю    | Bias resistor bump Connects to 1 kOhms ± 1% precision resistor on board                   |

| PCIE8_REF_CLKN     | I    | Reference clock differential pair                                                         |

| PCIE8_REF_CLKP     | I    | Reference clock differential pair                                                         |

| PCIE8_RXN[7:0]     | I    | Receive data differential pair                                                            |

| PCIE8_RXP[7:0]     | I    | Receive data differential pair                                                            |

| PCIE8_TXN[7:0]     | 0    | Transmit data differential pair                                                           |

| PCIE8_TXP[7:0]     | 0    | Transmit data differential pair                                                           |

#### 5.1.2.2 PCle x4

## Table 5-3 PCle x4 pins

| Pin name             | Туре | Description                                                                                                   |

|----------------------|------|---------------------------------------------------------------------------------------------------------------|

| PCIE4_0_AMON         | 0    | Analog monitor bump  NOTE: Reserved in BE-M1000 manufactured since 2021.                                      |

| PCIE4_0_ATT_BUT      | I    | Indicates whether the system attention button is pressed  NOTE: Reserved in BE-M1000 manufactured since 2021. |

| PCIE4_0_ATT_IND[1:0] | 0    | Controls the system attention indicator  NOTE: Reserved in BE-M1000 manufactured since 2021.                  |

| PCIE4_0_CMD_INT      | I    | Hot-plug controller command completed interrupt  NOTE: Reserved in BE-M1000 manufactured since 2021.          |

| PCIE4_0_DMON         | 0    | NOTE: Reserved in BE-M1000 manufactured since 2021.                                                           |

| PCIE4_0_DMONB        | 0    | NOTE: Reserved in BE-M1000 manufactured since 2021.                                                           |

| PCIE4_0_INTRL_CTRL   | 0    | NOTE: Reserved in BE-M1000 manufactured since 2021.                                                           |

| PCIE4_0_INTRL_ENG    | I    | System Electromechanical Interlock Engaged  NOTE: Reserved in BE-M1000 manufactured since 2021.               |

| Pin name             | Туре | Description                                                                                                                                          |

|----------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCIE4_0_MRL_SENS     | I    | MRL sensor state Indicates the state of the MRL sensor:  • 0: MRL is closed  • 1: MRL is opened  NOTE: Reserved in BE-M1000 manufactured since 2021. |

| PCIE4_0_PRES_ST      | I    | Presence detect state  NOTE: Reserved in BE-M1000 manufactured since 2021.                                                                           |

| PCIE4_0_PWR_CTRL     | 0    | Controls the system power controller  NOTE: Reserved in BE-M1000 manufactured since 2021.                                                            |

| PCIE4_0_PWR_FAULT    | I    | Power fault detect  NOTE: Reserved in BE-M1000 manufactured since 2021.                                                                              |

| PCIE4_0_PWR_IND[1:0] | 0    | Controls the system power indicator  NOTE: Reserved in BE-M1000 manufactured since 2021.                                                             |

| PCIE4_0_RBIAS        | Ю    | Bias resistor bump Connects to 1 kOhms ± 1% precision resistor on board                                                                              |

| PCIE4_0_REF_CLKN     | I    | Reference clock differential pair                                                                                                                    |

| PCIE4_0_REF_CLKP     | I    | Reference clock differential pair                                                                                                                    |

| PCIE4_0_RXN[3:0]     | I    | Receive data differential pair                                                                                                                       |

| PCIE4_0_RXP[3:0]     | I    | Receive data differential pair                                                                                                                       |

| PCIE4_0_TXN[3:0]     | 0    | Transmit data differential pair                                                                                                                      |

| PCIE4_0_TXP[3:0]     | 0    | Transmit data differential pair                                                                                                                      |

| PCIE4_1_AMON         | 0    | Analog monitor bump  NOTE: Reserved in BE-M1000 manufactured since 2021.                                                                             |

| PCIE4_1_ATT_BUT      | I    | Indicates whether the system attention button is pressed  NOTE: Reserved in BE-M1000 manufactured since 2021.                                        |

| PCIE4_1_ATT_IND[1:0] | 0    | Controls the system attention indicator  NOTE: Reserved in BE-M1000 manufactured since 2021.                                                         |

| PCIE4_1_CMD_INT      | I    | Hot-plug controller command completed interrupt  NOTE: Reserved in BE-M1000 manufactured since 2021.                                                 |

| PCIE4_1_DMON         | 0    | Differential digital monitor bump <b>NOTE:</b> Reserved in BE-M1000 manufactured since 2021.                                                         |

| PCIE4_1_DMONB        | 0    | Differential digital monitor bump <b>NOTE:</b> Reserved in BE-M1000 manufactured since 2021.                                                         |

| PCIE4_1_INTRL_CTRL   | 0    | Electromechanical Interlock Control  NOTE: Reserved in BE-M1000 manufactured since 2021.                                                             |

| PCIE4_1_INTRL_ENG    | I    | System Electromechanical Interlock Engaged  NOTE: Reserved in BE-M1000 manufactured since 2021.                                                      |

| PCIE4_1_MRL_SENS     | I    | MRL sensor state Indicates the state of the MRL sensor:  • 0: MRL is closed  • 1: MRL is opened  NOTE: Reserved in BE-M1000 manufactured since 2021. |

| Pin name             | Туре | Description                                                                               |

|----------------------|------|-------------------------------------------------------------------------------------------|

| PCIE4_1_PRES_ST      | I    | Presence detect state  NOTE: Reserved in BE-M1000 manufactured since 2021.                |

| PCIE4_1_PWR_CTRL     | 0    | Controls the system power controller  NOTE: Reserved in BE-M1000 manufactured since 2021. |

| PCIE4_1_PWR_FAULT    | I    | Power fault detect  NOTE: Reserved in BE-M1000 manufactured since 2021.                   |

| PCIE4_1_PWR_IND[1:0] | 0    | Controls the system power indicator  NOTE: Reserved in BE-M1000 manufactured since 2021.  |

| PCIE4_1_RBIAS        | Ю    | Bias resistor bump Connects to 1 kOhms ± 1% precision resistor on board                   |

| PCIE4_1_REF_CLKN     | I    | Reference clock differential pair                                                         |

| PCIE4_1_REF_CLKP     | ı    | Reference clock differential pair                                                         |

| PCIE4_1_RXN[3:0]     | ı    | Receive data differential pair                                                            |

| PCIE4_1_RXP[3:0]     | I    | Receive data differential pair                                                            |

| PCIE4_1_TXN[3:0]     | 0    | Transmit data differential pair                                                           |

| PCIE4_1_TXP[3:0]     | 0    | Transmit data differential pair                                                           |

#### 5.1.2.3 USB 3.0/2.0

## Table 5-4 USB 3.0/2.0 controller pins

| Pin name     | Туре | Description                                                                                                                                                                                                                                                                                                       |

|--------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB2_2_CTRL  | 0    | Port power control                                                                                                                                                                                                                                                                                                |

| USB2_2_DM0   | Ю    | USB D- signal. In normal operation, it carries USB data to and from the USB 2.0 PHY. In <i>High-Speed</i> ( <b>HS</b> ) operation, receives/transmits a maximum of 800 mV or 400 mV nominally. In <i>Full-Speed</i> ( <b>FS</b> ) or <i>Low-Speed</i> ( <b>LS</b> ) operation, receives/transmits 3.3 V nominally |

| USB2_2_DP0   | Ю    | USB D+ signal. In normal operation, it carries USB data to and from the USB 2.0 PHY. In HS operation, receives/transmits a maximum of 800 mV or 400 mV nominally. In FS or LS operation, receives/transmits 3.3 V nominally                                                                                       |

| USB2_2_ID0   | Ю    | USB mini-receptacle identifier or alternate test point for DC points probes inside USB 2.0 PHY                                                                                                                                                                                                                    |

| USB2_2_OVCUR | I    | Port overcurrent                                                                                                                                                                                                                                                                                                  |

| USB2_2_RT    | Ю    | Transmitter resistor tune  Connects to an external resistor (200 ± 1% Ohms) that adjusts the USB 2.0 PHY's high-speed source impedance                                                                                                                                                                            |

| USB2_2_VBUS0 | Α    | USB 5 V signal. This is the USB 5 V supply. A charge pump external to the USB 2.0 PHY must provide power to him. The nominal voltage is 5 V                                                                                                                                                                       |

| USB2_2_XI    | I    | Crystal oscillator XI                                                                                                                                                                                                                                                                                             |

| USB2_2_XO    | ı    | Crystal oscillator XO or board reference clock input  NOTE: When the reference clock source is a crystal, XO is a connection to a crystal. When the reference clock source is an external board clock, XO is an input. For modeling and simulation purposes, XO is declared as a pure input.                      |

| Pin name       | Туре | Description                                                                                                                                                                                                                                                                                  |

|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB2_3_CTRL    | 0    | Port power control                                                                                                                                                                                                                                                                           |

| USB2_3_DM0     | Ю    | USB D- signal. In normal operation, it carries USB data to and from the USB 2.0 PHY. In HS operation, receives/transmits a maximum of 800 mV or 400 mV nominally. In FS or LS operation, receives/transmits 3.3 V nominally                                                                  |

| USB2_3_DP0     | Ю    | USB D+ signal. In normal operation, it carries USB data to and from the USB 2.0 PHY. In HS operation, receives/transmits a maximum of 800 mV or 400 mV nominally. In FS or LS operation, receives/transmits 3.3 V nominally                                                                  |

| USB2_3_ID0     | Ю    | USB mini-receptacle identifier or alternate test point for DC points probes inside USB 2.0 PHY                                                                                                                                                                                               |